# Verification of Fiasco's IPC implementation

MASTER THESIS Number 560

by

E.G.H. Schierboom

$<\!\!{\rm eschierb@sci.kun.nl}\!>$

$\operatorname{at}$

Radboud Universiteit Nijmegen Computing Science Department Toernooiveld 1 6525 ED Nijmegen Holland

supervised by

dr. M.C.J.D. van Eekelen dr. J.E.W. Smetsers dr. W. Tews

June 21, 2007

# Abstract

Software nowadays is often designed with dependability in mind. Our thesis combines two approaches in creating a more dependable system: using microkernels instead of monolithic kernels and formally verifying software. We have tried to verify three properties of inter-process communication in the Fiasco microkernel. As Fiasco has been written in C++, which does not support verification, we converted the source code to a model in the PVS proof system. To keep the model and proofs compact, we abstracted away many details of inter-process communication.

Two of the three properties were verified; both dealt with threads possibly waiting forever. The third property, verification of the assertions in the source code, posed several problems. One problem proved insurmountable, probably due to the abstractions applied. Another problem led to the finding of a bug in Fiasco's IPC implementation. Although finding the bug had clear, practical use, we consider the fact that our abstract model could find the bug more important. It shows that one does not have to create a one-on-one model to apply (partial) verification; even our model in which essential components were abstracted away sufficed to find a bug.

# Preface

To me, computers are fascinating machines in all their aspects. I have always favored software over hardware though, writing my own software was what got me into studying computer science after all. Even though computers play a vital role in society nowadays, one must not forget that computer science is a relatively young field of research<sup>1</sup>. It is therefore not surprising that there are still many problems with computers, although progress is being made rapidly (which is another interesting aspect of computer science). As hardware leaps forward<sup>2</sup>, the general impression is that the software lags behind. This impression stems from the fact that most problems with computers are due to the software running on them.

Lately, one of the most interesting developments in writing software, at least to me, has been the shift in focus from performance to dependability<sup>3</sup>. This shift can, for a large part, be attributed to the changing needs of people. Where one was previously happy that a computer could execute a task, people are now so accustomed to computers that they expect that task to be executed dependably. Unfortunately, if one would ask a random person if he or she has had any bad experiences with the dependability of software, chances are very high that most would answer with a resounding "yes". The prime example of software not being dependable is when it, or the whole system, crashes.

Almost all software on business or private computers runs on top of (and thus depends on) an operating system, the most well known probably being Microsoft Windows, Unix/Linux and Mac OS. To me, operating systems are the most interesting pieces of software available because of their vital role and the very diverse tasks they execute. When one wants to create dependable software (which relies on the operating system), it makes sense to create a dependable operating system. In an operating system, the most vital part (or "heart") is the kernel, which dependability is therefore absolutely critical.

In line with the desire to create dependable software, verification of software is a rapidly expanding field of computer science. What can be better to its dependability than to formally verify that a piece of software does what it is supposed to do? In our thesis, we will combine both our interest in operating system kernels and software verification. Our research shows how one can verify (a part of) a real kernel. This is particularly useful as kernels are among the most likely candidates for verification because of their vital role. We hope that our thesis will kindle your interest in verification of software, as we expect it to become an integral part of software development in the, hopefully near, future.

<sup>&</sup>lt;sup>1</sup>Especially when compared to other exact sciences such as mathematics and physics, which predate it by many centuries.

$<sup>^{2}</sup>$ Processors are an obvious example, as Moore's law has successfully been applied to them for the last 30 years.

<sup>&</sup>lt;sup>3</sup>Which loosely translates to software behaving like one expects it to.

# Acknowledgements

In writing this thesis, I have received help from a great many people. First and foremost I would like to thank Marko van Eekelen, Hendrik Tews and Sjaak Smetsers for the great assistance they have given me. They have helped me with many different aspects of this thesis, from the verification of individual lemmas to planning the research itself. Secondly, I want to thank René Reusner and Adam Lackorzynski for never becoming tired of answering all my questions regarding the Fiasco IPC implementation. In this regard, the L4 hackers mailinglist has also been very helpful; their responses were always fast and to the point. The structure and contents of this document have been extensively commented upon by Jens Wagemakers, for which I owe him many thanks. For a more general discussion of my thesis I often turned to Sietse Overbeek, with whom I had some very useful discussions. When a technical problem arose, Engelbert Hubbers was always quick to solve it.

Besides the abovementioned people, who were directly involved with the thesis' contents, I have also received support from a lot of people that did not involve the contents of this thesis. Most notably, these include my friends, colleagues and family and of course my girlfriend, Jeltine Jungheim. I want to specifically mention my dad who has always supported me in whatever I did, but unfortunately passed away far too young; this thesis is dedicated to him.

I hereby apologize to anyone that has not made it in this list, that does not mean I did not appreciate your help but merely that my memory has failed me.

# Contents

| 1 | Intr        | oduction     |                                  | 16              |

|---|-------------|--------------|----------------------------------|-----------------|

| 2 | Backgrounds |              |                                  |                 |

|   |             |              | oftware dependability            | 18              |

|   |             |              | language                         | 18              |

|   |             |              | e verification                   | 19              |

|   |             |              | mized kernel                     | $19^{-5}$       |

|   |             |              | tion                             | 20              |

|   | 2.2         |              | nel                              | $\frac{-0}{21}$ |

|   |             |              | duction                          | $\frac{-1}{21}$ |

|   |             |              | gn                               | 21              |

|   |             | C            | ementations                      | $\frac{-1}{23}$ |

|   | 2.3         | - I          |                                  | $\frac{-0}{24}$ |

|   |             |              | duction                          | 24              |

|   |             |              | Dry                              | $\overline{24}$ |

|   |             |              | ads                              | 24              |

|   |             |              | hronization                      | 26              |

|   |             | •            | s                                | $\frac{20}{26}$ |

|   |             |              | eouts                            | $\frac{20}{27}$ |

|   |             |              |                                  | $\frac{21}{27}$ |

|   | 2.4         |              |                                  | 32              |

|   | 2.1         |              | duction                          | 32              |

|   |             |              |                                  | 33              |

|   |             |              | nple proof                       | 33              |

|   | 2.5         |              | k                                | 35              |

|   | 2.0         |              | ying memory management in Fiasco | $\frac{35}{35}$ |

|   |             | •            | loping a C++ semantics compiler  | $\frac{35}{35}$ |

|   |             |              | ying IPC in Fiasco               | $\frac{35}{35}$ |

|   |             | •            | oved IPC path                    | 36              |

|   |             | -            | erified                          | 36              |

|   |             | 2.0.0 14.00  |                                  | 00              |

| 3 | Mo          | del creation |                                  | 38              |

|   | 3.1         | Modeling ap  | proach                           | 38              |

|   | 3.2         |              | *                                | 38              |

|   |             |              | erties                           | 39              |

|   |             | 3.2.2 Absti  | ractions                         | 39              |

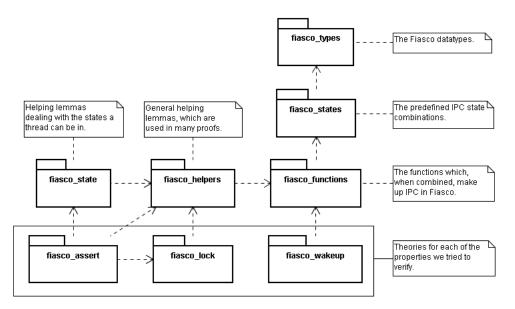

|   |             |              | bry structure                    | 40              |

|   |             |              | co types                         | 41              |

|   |             |              | co functions                     | 44              |

|   |             |              | ting functions                   | 48              |

|   |             | -            | mption points                    | 49              |

| 4 | Mo                       | del vei                            | rification                                                                                                                                                                                                                                                                                                                         | <b>53</b>                                                                                      |

|---|--------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|   | 4.1                      | Verific<br>4.1.1<br>4.1.2<br>4.1.3 | cation attempts       Property 1: removal of sender's thread lock on receiver         Property 1: removal of sender's thread lock on receiver       Property 2: waking up receiver in combined send/receive         Property 2: waking up receiver in combined send/receive       Property 3: validation of assertions in the code | 53<br>53<br>55<br>56                                                                           |

| 5 | <b>Dis</b><br>5.1<br>5.2 | cussion<br>Gener                   | · ·                                                                                                                                                                                                                                                                                                                                | <b>67</b><br>67<br>68                                                                          |

| 6 | Cor<br>6.1<br>6.2        | Concl                              | ns and future work usions e work Further verification Modular proofs Automation of verification Improved conversion                                                                                                                                                                                                                | <ul> <li>71</li> <li>71</li> <li>72</li> <li>72</li> <li>73</li> <li>73</li> <li>73</li> </ul> |

| A | open                     | dix A                              | PVS: fiasco_types.pvs                                                                                                                                                                                                                                                                                                              | <b>74</b>                                                                                      |

| A | open                     | dix B                              | PVS: fiasco_functions.pvs                                                                                                                                                                                                                                                                                                          | 77                                                                                             |

| A | open                     | dix C                              | PVS: fiasco_states.pvs                                                                                                                                                                                                                                                                                                             | 90                                                                                             |

| A | open                     | dix D                              | PVS: fiasco_helpers.pvs                                                                                                                                                                                                                                                                                                            | 92                                                                                             |

| A | open                     | dix E                              | PVS: fiasco_state.pvs                                                                                                                                                                                                                                                                                                              | 97                                                                                             |

| A | open                     | dix F                              | PVS: fiasco_lock.pvs                                                                                                                                                                                                                                                                                                               | 102                                                                                            |

| A | open                     | dix G                              | PVS: fiasco_wakeup.pvs                                                                                                                                                                                                                                                                                                             | 106                                                                                            |

| A | open                     | dix H                              | PVS: fiasco_assert.pvs                                                                                                                                                                                                                                                                                                             | 107                                                                                            |

| A | open                     | dix I                              | C++: thread-ipc.cpp                                                                                                                                                                                                                                                                                                                | 110                                                                                            |

| A | open                     | dix J                              | C++: sender.cpp                                                                                                                                                                                                                                                                                                                    | 124                                                                                            |

| A | open                     | dix K                              | C++: receiver.cpp                                                                                                                                                                                                                                                                                                                  | 126                                                                                            |

# List of Figures

| 2.1 | Fiasco IPC roles diagram.     | 27 |

|-----|-------------------------------|----|

| 2.2 | IPC overview.                 | 28 |

| 2.3 | IPC send part overview.       | 29 |

| 2.4 | IPC receive part overview.    | 29 |

| 2.5 | Fiasco interrupt transitions. | 32 |

| 0.1 |                               | 10 |

| 3.1 | PVS theories structure.       | 40 |

# List of Tables

| 2.1 | Overview of several L4 implementations                    | 24 |

|-----|-----------------------------------------------------------|----|

| 2.2 | Mapping of L4 IPC calls to Fiasco send and receive parts. | 28 |

|     |                                                           |    |

| 3.1 | Model: split functions                                    | 48 |

# List of Sources

| 2.1  | PVS: example of the extensible records mechanism                   |

|------|--------------------------------------------------------------------|

| 3.1  | PVS: sender list definition                                        |

| 3.2  | PVS: thread state definition. 41                                   |

| 3.3  | C++: $Thread\_ipc\_sending\_mask$ state definition                 |

| 3.4  | PVS: Thread_ipc_sending_mask state definition                      |

| 3.5  | PVS: context, sender and receiver definitions                      |

| 3.6  | PVS: thread definition                                             |

| 3.7  | PVS: thread alternative definition                                 |

| 3.8  | PVS: thread pointer definition                                     |

| 3.9  | PVS: definition of thread list                                     |

|      | PVS: IPC error codes- and timeout definitions                      |

|      | PVS: an example of a system state-modifying function               |

|      | PVS: incomplete system state, focusing on threads                  |

|      | PVS: example of accessing this thread                              |

|      | PVS: definition of special this pointer type                       |

|      | PVS: incomplete system state, with integrated error field          |

| 3.16 | PVS: example of error setting and checking                         |

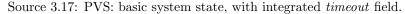

| 3.17 | PVS: basic system state, with integrated <i>timeout</i> field      |

|      | PVS: system state initialization in the $sys_ipc()$ function       |

|      | PVS: $sender_ok()$ function without implementation                 |

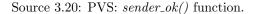

|      | PVS: $sender_ok()$ function                                        |

|      | C++: $sender_ok()$ function                                        |

|      | PVS: calling the split $ipc\_receiver\_ready()$ function           |

|      | PVS: preemption_action type                                        |

| 3.24 | PVS: preemption_action() function                                  |

|      | PVS: expanded system state, with added <i>seed</i> field           |

|      | PVS: preemption_point() function                                   |

|      | PVS: preemption_point_actions() function                           |

| 3.28 | PVS: <i>ipc_receiver_ready()</i> function                          |

| 4.1  | PVS: $lock_dirty()$ function                                       |

| 4.2  | PVS: clear_dirty() and clear_dirty_dont_switch() functions         |

| 4.3  | PVS: basic system state, with integrated handshake_attempted field |

| 4.4  | PVS: setting the <i>handshake</i> field                            |

| 4.5  | PVS: property 1, formal definition                                 |

| 4.6  | PVS: $in_i pc()$ definition                                        |

| 4.7  | PVS: property 2, formal definition                                 |

| 4.8  | PVS: basic system state, with added <i>assertions_held</i> field   |

| 4.9  | C++: have_receive assertion                                        |

|      | PVS: have_receive assertion                                        |

|      | PVS: property 3, formal definition                                 |

|      | PVS: thread_polling assertion                                      |

| 4.13 | PVS: try_handshake_receiver_no_error_not_polling lemma             |

|      |                                                                    |

| 4.14 | PVS: try_handshake_receiver() problematic lines.                     | 58 |

|------|----------------------------------------------------------------------|----|

| 4.15 | C++: thread_polling bit, added assertion.                            | 59 |

| 4.16 | PVS: unset <i>thread_polling()</i> bit invariant.                    | 59 |

| 4.17 | PVS: unset <i>thread_polling()</i> bit invariant.                    | 59 |

| 4.18 | PVS: do_send_wait() function, problematic thread_polling path.       | 60 |

|      | PVS: the axiom used in the <i>do_send_wait()</i> function            |    |

| 4.20 | PVS: preemption_actions()- and related receiver_ready() lemma        | 61 |

| 4.21 | PVS: receiver_ready()- and dependent preemption_actions() lemma      | 61 |

|      | PVS: the axiom used in the $do\_send\_wait\_loop()$ function         |    |

| 4.23 | PVS: property 3, sublemma for the <i>do_ipc_send_part()</i> function | 62 |

# Chapter 1

# Introduction

"To err is human - and to blame it on a computer is even more so."

Robert Orben

"I do not fear computers. I fear the lack of them."

Isaac Asimov

Writing computer programs has changed a lot in the last decennia. The programs written for the first computers had to keep in mind that its resources (such as processing power and memory) were very limited and thus efficiency was a key design goal. As computers advanced, its resources became more abundant so efficiency became less an issue. Instead, as reliance on computers increased, building a more dependable system became a key design goal. The concept of dependability is defined by the IFIP<sup>1</sup> [IF105] as follows:

"The notion of dependability, defined as the trustworthiness of a computing system which allows reliance to be justifiably placed on the service it delivers, enables these various concerns to be subsumed within a single conceptual framework. Dependability thus includes as special cases such attributes as reliability, availability, safety, security."

To create a dependable computer system it makes sense to start looking at the foundations of the software running on a computer, namely the kernel. Critical functions such as memory allocation, scheduling, process management<sup>2</sup> and inter-process communication (IPC) are all handled by the kernel. Errors in the kernel decrease its dependability and without a dependable kernel we cannot reasonably expect the whole system to be dependable<sup>3</sup>. One of the main issues in creating a dependable system is thus: how to create a dependable kernel?

One approach to create a dependable kernel is to make it a microkernel. The main design motivation when designing a microkernel is summarized by Jochen Liedtke in [Lie95]:

"[...] a concept is tolerated inside the microkernel only if moving it outside the kernel [...] would prevent the implementation of the system's required functionality."

A microkernel is thus a specific type of kernel in which anything that does not necessarily belong in the kernel is moved outside the kernel. This results in a smaller and more robust system. A monolithic kernel however includes, often many, concepts that do not necessarily belong in the kernel. A typical

<sup>&</sup>lt;sup>1</sup>The International Federation For Information Processing.

$<sup>^{2}</sup>$ Such as the creation and stopping of processes. A process is sometimes also referred to as a task.

$<sup>^3\</sup>mathrm{Remember}$  that each task relies on the kernel for its core functionality.

concept that a monolithic kernel includes but a microkernel does not is the file server (or file system). The main benefit of including a concept in the kernel is improved performance, as switching between user- and kernel-mode is quite expensive [HHL+97]. Its main disadvantage is that a crash of the concept often brings down the entire kernel (and thus the entire system). When a concept resides in user space, a crash of that concept has a significantly smaller chance of bringing down the entire system as it cannot directly access the kernel space (in which the kernel resides).

Although a microkernel is more compact than a monolithic kernel, errors are still likely to exist. Each error in the kernel negatively influences its dependability, the question is therefore: how to minimize the number of errors in the kernel? One approach is to formally verify the kernel. Formally verifying software is very similar to creating a mathematical proof<sup>4</sup>. Just as a mathematical proof lets you say things with absolute certainty about the proven statement, formal software verification lets you say things with absolute certainty about the verified software. Being able to guarantee that certain properties hold when executing software is incredibly helpful in developing a dependable system; one could for example verify that the system will never be in a certain, erroneous state.

This thesis will report on our attempt to formally verify a part of the Fiasco microkernel, which is based on Jochen Liedtke's L4 microkernel specification [Lie96] and has been developed by the Technische Universität Dresden. We will try to formally verify certain aspects of inter-process communication in Fiasco. Our research question is as follows:

#### What properties of inter-process communication on the Fiasco microkernel can be proven?

The verification will be done by creating a model of inter-process communication in Fiasco and then verify properties of that model. The verification system PVS<sup>5</sup> will be used to verify and create the model. We have chosen specifically for Fiasco because it is the subject of a larger verification project, called VFiasco [HTS03], in which our research can easily be integrated. PVS has been chosen mainly because it has thus far been the verification system of choice in the VFiasco project.

After this short introduction into the problem area, we continue at chapter two with the thesis' backgrounds. Chapter three discusses how the PVS model was created. The verification of several properties of the model is detailed in chapter four. A discussion of the obtained results is presented in chapter five and in the sixth and final chapter conclusions and suggestions for future work are presented.

$<sup>^4\</sup>mathrm{Computerized}$  mechanical proofs are often regarded upon with high scepticism by mathematicians though.  $^5\mathrm{Prototype}$  Verification System.

# Chapter 2

# Backgrounds

"There are two ways of constructing a software design; one way is to make it so simple that there are obviously no deficiencies, and the other way is to make it so complicated that there are no obvious deficiencies. The first method is far more difficult."

C. A. R. Hoare

"Beware of bugs in the above code; I have only proved it correct, not tried it."

Donald Knuth

# 2.1 Improving software dependability

Dependability (of which security is a special case) has become more and more important of late. The definition of dependability has been given in the introduction, so we will now focus on how to create dependable software. There are many approaches on how to create dependable software; we will list those we consider to be the most important. Please note that the proposed solutions are not mutually exclusive, in fact some of them have already been combined  $[HTS03, HLA^+05]$ .

#### 2.1.1 Safe language

A lot of software errors are not due to incorrect designs, but due to incorrect programming. The most well known problem is probably that of a *buffer overflow*. Two of the most used languages, C and C++, offer no inherent protection against buffer overflows and are thus vulnerable to this type of memory error. A solution is to design a language that is memory safe, which means that no buffer overflows can occur. Examples of these languages are C# and Java. The problem with these languages is that they offer no fine-grained control over memory (de)allocation, which is needed for common performance optimizations to be applied.

As maximizing performance is still vital to many programs (such as device drivers, computer games or kernels), these safe languages are often not an option. The approach taken by Cornell University was to develop a dialect of C, named Cyclone  $[JMG^+02]$ , which preserves its syntax and semantics, but also prevents some of the most common errors in the C language (such as the aforementioned buffer overflow) by using new (albeit very similar) syntax.

Another approach is to define a completely new, safe language. This approach is taken by the John

Hopkins University in their Coyotos project [Uni06]. They have developed a safe language, called BitC [JS06], with fully specified semantics. Their approach is directly related to the next solution for a dependable system: code verification.

#### 2.1.2 Code verification

One of the most rigorous methods to improve the dependability of software is to verify its correctness. Verification of code is done by first creating a specification of the code in a verification language and then use that language's verification capabilities to verify the required properties<sup>1</sup>. Examples of verification languages, which are specifically tailored to constructing proofs, are PVS [Owr], Isabelle/HOL [NPW02], BoogiePL [DL05] and Abstract Machine Notation [SN01].

The problem with specifying code in a verification language is that often no executable code can be generated from it. To still be able to prove properties of executable code, there are two options: convert the verification language to an executable language or vice versa. For both options it is of vital importance that the conversion retains the exact semantics of the source language, otherwise the proofs would not necessarily apply to the corresponding source code or the executable code might not do what the source specification said it would do. The problem with a semantics-retaining conversion is that both languages need to have a clear and well-defined semantics. Unfortunately, the widely used C++ language lacks in this area. Although attempts have been made to develop a clear and well-defined semantics for C++ (which will be discussed later in this chapter), the results so far are still lacking in their applicability to real-world scenarios. The Java language though *does* have a well-defined semantics; the LOOP compiler [vdBJ01] proved that it was feasible to automatically convert Java to a higher-order logic. As a demonstration of its applicability to real-world code, Huisman et. al. used the LOOP compiler to successfully verify a non-trivial property of Java's Vector class [HJvdB99]. Unfortunately, the LOOP compiler is not yet generally applicable as it currently does not support threads<sup>2</sup>.

Even if one has verified properties of source code, it is ultimately the machine code that gets executed. Therefore, it is the machine code that ultimately has to be verified. If one assumes that the conversion from source code to machine code, which is done by the compiler, retains semantics, verification of the source code suffices. Curzon described in [Cur92] how a compiler can be verified.

As said, conversion from certain languages (such as C++) to a verification language has proven to be very hard. An alternative to an automated conversion is to create a model of the source code in the verification language. This has two clear problems; first of all the conversion needs to be done *by-hand* most of the time, which is a far more tedious and error-prone operation than automatic conversion, and secondly there can be no guarantee that proofs in the verification language apply to the source code (as the semantics of the model might not match those of the source code).

To assist the prover<sup>3</sup> reason about correctness, some languages support the use of source code annotations, which can be used in the verification language. Annotation systems have been developed for a wide variety of languages, such as C [EGHT94], Java [LBR99, HHJT98] and a dialect of C# called Spec# [BLS04].

### 2.1.3 Minimized kernel

The most important part of an operating system (OS) is the kernel, as it handles critical OS parts such as process communication, scheduling and memory management. There are basically two different types of kernels: monolithic- and microkernels. A monolithic kernel executes all its code in the same address space in order to improve performance, whereas a microkernel tries to execute as much of its

<sup>&</sup>lt;sup>1</sup>An example of such a property is requiring that the program always terminates.

$<sup>^{2}</sup>$ This is especially unfortunate considering the latest trend of developing multi-threaded applications, which is due to multi-processor systems becoming increasingly widespread.

<sup>&</sup>lt;sup>3</sup>The program with which proofs are constructed in a verification language.

functionality in user space. A microkernel can be seen as a minimized version of a monolithic kernel. The basic requirements for a microkernel are given in [Lie95].

Currently two types of microkernels are identified: first generation microkernels such as Mach [RJO+89] and Minix [HBG+06] and second generation microkernels such as QNX [Hil92] and Fiasco [HTS03]. First generation microkernels still contained code in the kernel which were not strictly necessary for executing its core tasks, second generation microkernels moved this code outside the kernel. Second generation microkernels are thus more *strict* microkernels.

Usually, a microkernel's tasks are limited to address space management, thread management and IPC. By restricting its functionality to these core concepts, a microkernel is typically much smaller than a monolithic kernel and thus less likely to contain bugs. Furthermore, the removal of many concepts from the kernel results in a system less likely to crash. Take for example the file server, a typical concept that is included in monolithic kernels (because of its importance on the performance of the kernel), but is not part of a typical microkernel. In the monolithic kernel, the file server has access to all kernel data; a crash of the file server can therefore result in a crash of the whole kernel (and thus everything running on the kernel). However, in the microkernel the file server executes in user space and cannot modify the kernel data. Therefore, a crash of the file server is not likely to crash the microkernel on which it is running.

#### 2.1.4 Isolation

Another way to create a more dependable system is to contain processes in small, isolated spaces. When a process is isolated, it cannot do any harm to other (isolated) processes. There are two types of isolated processes: software isolated processes (SIPs) and hardware isolated processes (HIPs)<sup>4</sup>. In practice, many operating systems do not enforce strict process isolation, which results in a system where programs can modify other programs, with potentially very damaging results (for example a single driver's failure crashes the whole system).

Hardware isolation of processes can be done by the OS, which limits a processes' memory access to specific pages of physical memory. The OS usually achieves this through standard hardware mechanisms, for example by running user processes in a less priviledged mode than kernel processes<sup>5</sup>. The mechanism an OS typically uses to hardware-isolate processes is virtual memory. Even though virtual memory is directly supported by most processors, studies show that this form of process isolation is in fact quite costly [AFH<sup>+</sup>06, MHH02].

Software isolation depends on the software to isolate processes. The Singularity operating system  $[HLA^+05]$  is designed with software isolation in mind and also heavily uses language safety  $[AFH^+06, FL06, HAB^+06]$ . In short, in Singularity each application runs in its own, private software *box*, which ensures that the application can only modify data in its own box.

Another form of software isolation is called virtualization. Normally the OS is the lowest software layer on a system, but virtualization adds another layer below the OS. Each virtualized OS thinks it has access to all hardware, but in fact hardware access is controlled by the virtualization layer. The process that manages the virtualization of hardware is often referred to as the *hypervisor*<sup>6</sup>. Now several OSes (and its processes) can run simultaneously without interfering with each other (although the hypervisor might allow some limited and controlled communication between OSes), because the hypervisor ensures that an OS cannot access the hardware issued to another OS.

Traditionally, virtualization of x86 processors is hard as the x86 architecture does not meet the Popek and

<sup>&</sup>lt;sup>4</sup>The terms SIP and HIP are taken from  $[AFH^+06]$ .

<sup>&</sup>lt;sup>5</sup>On x86 processors, processes running at ring 0 are given full control of the processor and lower rings have limited access. <sup>6</sup>This is a reference to the OS sometimes being referred to as a supervisor. Obviously the virtualization layer has more control than the OS, therefore the term hypervisor as it supersedes supervisor.

Goldberg virtualization requirements [PG74]. The main x86 processor manufacturers, AMD and Intel, acknowledged the problems with virtualization and have recently built extensions in their processors to support virtualization<sup>7</sup>. The virtualization layer can now translate the *difficult* OS calls to alternative, virtualization suitable calls, resulting in better virtualization performance.

Another way to deal with the *difficult* system calls is to apply paravirtualization. This means that the OS is modified to the extent that no *difficult* calls will be made, therefore no processor-specific virtualization extensions have to be used. Unfortunately, OS modification is not possible for closed-source systems without their creators' explicit consent.

# 2.2 L4 microkernel

#### 2.2.1 Introduction

A performance analysis of first generation microkernels, such as Mach, revealed that they failed to deliver a high performance microkernel [HHL<sup>+</sup>97]. Jochen Liedtke realized that one of the key reasons why Mach did not perform very well, was its complex IPC implementation. He then set himself to creating a microkernel specification that *would* offer high performance; this resulted in the L3 microkernel specification [Met96]. The L3 specification had a small and efficient IPC specification, which indeed offered massive performance gains when compared to earlier microkernels such as Mach. However, Liedtke noted that the specification still contained concepts that could (and should) be moved out of the microkernel. The removal of these concepts resulted in the L4 specification. By definition the L4 microkernel specification is thus a second generation microkernel<sup>8</sup>.

The original L4 microkernel specification is the L4.V2 specification [Lie96]. When the L4 specification is referred to, one usually refers to the L4.V2 specification. However, the L4.V2 specification had some problems associated with it. One of the biggest problems was with the thread ids. The thread ids as specified in L4.V2 were found to be rather inflexible and unwieldy. Another problem was that the *clans and chiefs* concept<sup>9</sup> was too inefficient for most purposes. These problems (and more) were addressed in the L4.V2 specification [Lie99]. The main goal of this specification was not to solve all problems of the L4.V2 specification, but to use it as an experimental test-case. The aim of the L4.X2 release [Lie04] though was to solve the problems in the L4.V2 specification. Some of the more notable differences between the L4.V2- and L4.X2 specifications are: the separation of task- and thread management, support for multiprocessing and a clear separation between API<sup>10</sup> and ABI<sup>11</sup>. Lastly, Kauer and Völp from the Technische Universität Dresden have developed the L4.Sec specification [BK05], which enhances the L4 specification with security features.

### 2.2.2 Design

Although the L4 kernel is created with minimalism in mind, there are a couple of basic concepts that have to be in the kernel:

- Address spaces

- Threads

- Inter-process communication

<sup>&</sup>lt;sup>7</sup>Respestively called AMD Virtualization [AMD05] and Intel Virtualization Technology [Cor05].

$<sup>^{8}</sup>$ As mentioned, a second generation microkernel is designed with both minimalism and performance in mind.

$<sup>^{9}</sup>$ The clans and chiefs concept was designed to enable the implementation of arbitrary security policies.

$<sup>^{10}</sup>$ Application Programming Interface. The API is the source code interface with which a computer program or library lets other programs or libraries use its services.

<sup>&</sup>lt;sup>11</sup>Application Binary Interface. An ABI allows object code to be run without changes on any system using a compatible ABI.

- Mapping

- Scheduling

Address spaces An address space is a set of mappings from virtual- to physical memory. Address spaces form the mechanism through which task-isolation<sup>12</sup> is achieved. A flexpage is a contigous region of virtual address space.

**Threads** A thread is the single unit of execution. Each thread belongs to a single address space, with a predefined maximum number of threads per address space. An L4 thread is characterized by a set of registers, with the instruction pointer, stack pointer and state information being required and stored in the kernel in a structure called the thread control block (TCB<sup>13</sup>).

**Inter-process communication** The sole mechanism through which threads can communicate and exchange data is inter-process communication, which as a side-effect also increases independence between system components. IPC in L4 is always synchronous, which means that no data is exchanged unless both parties agree to. IPC is also unbuffered; the kernel does not temporarily store messages which are to be sent later. L4 offers two different types of IPC: short- and long IPC. Short IPC does not involve access of user space memory and thus cannot generate page-faults; long IPC *does* access user space memory and thus has to take possible page-faults into account. Short IPC only allows a limited amount of data to be be sent, messages exceeding the short IPC limit have to be sent using long IPC. When possible, short IPC is used as it offers significant performance benefits. The IPC mechanism is also used to handle both hardware- and software- interrupts<sup>14</sup> and to map-, grant and unmap flexpages. A timeout can be set to enable (unsuccessful) IPC operations to be cancelled after a specified time.

**Mapping** When a page-fault is generated in a thread's address space, a notification is sent to the thread's associated pager (which can be different for each thread); that pager can then insert a memory page to resolve the page-fault. Threads can map-, grant- and unmap any of its flexpages to another thread. Mapping flexpages to another thread means that the flexpages will be shared between the mapper and the mappee. Granting a flexpage to another thread passes the control of that flexpage to the grantee, the granter afterwards cannot use the granted flexpage. The unmapping of a flexpage is the inverse operation of mapping a flexpage (it can only be invoked on mapped flexpages, not on granted flexpages). The mechanism through which this is possible is IPC, where a special IPC message is sent between the two threads involved in the memory mapping.

**Scheduling** The scheduling of threads in L4 is priority-based, which means that the ready thread with the highest priority is always the one to be allocated CPU-time. Each thread has a priority level (of which there are 256) and time quantum associated with it. Scheduling threads with the same priority level is done through a round-robin schedule<sup>15</sup>.

The L4 specification also mentions the concept of a *task*, but this is essentially equivalent to the concept of an address space. The main difference between a task and an address space is a conceptual one: the former focuses on the system's memory and the latter focuses on the threads running in an address space. The L4 definition of a task is the set of threads sharing an address space. Creating a new task results in the creation of an address space with one thread in it.

As one of the L4 design goals was to implement no policies, how memory is allocated is left to the application(s) running on L4; the kernel only provides the means to allocate memory. The L4 specification

$<sup>^{12}</sup>$ Task-isolation is the inability of tasks to tamper with the data of other tasks without their consent.

<sup>&</sup>lt;sup>13</sup>Not to be confused with Trusted Computing Base.

$<sup>^{14}</sup>$ An example of a software interrupt in L4 is a timeout.

$<sup>^{15}</sup>$ Round-robin scheduling lets the first thread of a list of waiting threads use the CPU for a period up to its time quantum. Should the thread not be finished when it's time quantum expires, the thread is moved to the end of the list and scheduling resumes with the first item of the list.

specifies though that the initial address space, called  $\sigma_0$ , should comprise all available memory (excluding kernel-reserved memory).

#### IPC

As said, IPC communication is always synchronous and unbuffered. Each IPC call therefore involves exactly one sender and one receiver. L4 offers five different IPC calls: *send*, *receive*, *wait*, *reply-wait* and *call*. An invocation of the send call results in the sending of a single message, after which the invoker continues his work. Invoking the receive call results in the invoker waiting to receive a message from *any* sender. The wait call does the same as the receive call, but only accepts messages from a single, specified sender. The last two calls are basically predefined combinations of the aforementioned calls, where each combination reflects a common real-world scenario. The call method results in the sending of a message after which the sender waits for a return message from the receiver it just sent the message to. The reply-wait operation is one in which a single message is sent after which the invoker waits for a reply from any source.

A real-world example in which both the call- and reply-wait operations are used is a webserver. The webserver handles a request from a client, returns the results to the client and is then ready to receive a request from any client; this is equal to the reply-wait operation. From the perspective of the client, a call operation is done as the client subsequently requests data from the webserver and waits for a response from that same webserver.

For performance guarantees, the L4 specification requires that the transitition between the send- and receive states in a single IPC call requires no time<sup>16</sup> (also referred to as an atomic switch). Having an optimized path for frequently used situations clearly benefits the system's real-world performance. Another result of combining the send and receive operations in the call and reply-wait methods is that it saves system calls (without the call method, both a send- and receive call would have to be made to achieve the same result). As Liedtke showed in [Lie93], the switching between user- and kernel mode as the result of a system call is very expensive. In both combined calls a single system call is saved, which helps to improve IPC performance.

## 2.2.3 Implementations

The original L4 implementation by Jochen Liedtke, sometimes referred to as L4/x86, was completely written in assembly language to maximize performance. Writing a program in assembly language has some obvious disadvantages, of which poor readability- and maintainability are probably the most important ones. Therefore, and because of licensing issues, the Technische Universität Dresden developed an L4based kernel in C++ named Fiasco, which demonstrated that an implementation of the L4 specification in a higher-level language was feasible. Apart from implementing the L4 specification, Fiasco also offers hard real-time support (which is not part of the L4 specification). Similarly, Jochen Liedtke and his team at the University of Karlsruhe developed L4Ka::Hazelnut, once again as proof that an L4 microkernel could be implemented in a higher level language and still offer high performance.

Up until this point, all L4 implementations were inheritly bound to the underlying architecture [Lie95]. This changed with the advent of the L4.X2 specification. One of the first implementations of the L4.X2 specification was also developed at Karlsruhe and was named L4Ka::Pistacchio. The main aim of Pistacchio was on both performance *and* portability. The new portability demand was clearly met by Pistacchio, as the supported platforms included Alpha-, ARM-, IA32-, MIPS- and PowerPC architectures. A relatively new specification and implementation originates from the National ICT Australia group. They have developed an L4 version specifically aimed at embedded systems called NICTA [Aus05].

<sup>&</sup>lt;sup>16</sup>This also protects the receiver (server) against Denial Of Service attacks.

| Implementation            | Versions | Architectures                         |

|---------------------------|----------|---------------------------------------|

| NICTA::Pistachio-embedded | N1, N2   | IA-32, ARM, Mips64                    |

| L4Ka::Pistacchio          | X2       | IA-32, IA-64, ARM, AMD64, PowerPC-32, |

|                           |          | PowerPC-64, Alpha, Mips64             |

| L4Ka::Hazelnut            | X0       | IA-32, ARM                            |

| Fiasco                    | V2, X2   | IA-32, ARM, AMD64, UX                 |

| L4/x86                    | V2, X0   | IA-32                                 |

Table 2.1: Overview of several L4 implementations

#### 2.3Fiasco

#### 2.3.1Introduction

The Fiasco kernel is based on the aforementioned L4 specification. Fiasco is a second generation microkernel, which means that it is created with minimalism (nothing exists in the kernel that cannot be moved out of it) and performance in mind. The effect of minimalism can clearly be seen in the number of lines of code the kernel comprises: around 20,000 lines of code for Fiasco compared to around 3.2 million for the Linux kernel. The Fiasco kernel is developed with real-time features in mind, which means that the system is fully preemptable<sup>17</sup>.

#### 2.3.2History

DROPS<sup>18</sup> [HBB+98] is a research project which aims to find design techniques to implement a distributed, real-time operating system where every component can guarantee a certain level-of-service to applications. The foundation of DROPS is based on the L4 specification. As the original L4/x86 implementation by Jochen Liedtke had some serious disadvantages (readability, maintainability and licensing issues), the Technische Universität Dresden decided to create their own implementation of the L4 specification, called Fiasco, which could be used by DROPS. Besides implementing the L4.V2 and L4.X2 specifications, Fiasco sets itself apart from other L4 implementations with its real-time features, obviously created with DROPS' real-time focus in mind.

Another project related to Fiasco is Fiasco-UX [Sch01], which is a port of the Fiasco microkernel to the Linux system-call interface. This means that Fiasco-UX can be run as an application on a Linux system and due to its special design (no need for kernel-level priviliges) it can even be run as a regular user-level application. One of the main benefits of this approach is its ease of use, particularly when developing applications for Fiasco. Rebooting the machine due to a (kernel) crash is no longer necessary, a simple restart of the Fiasco-UX process suffices. Another advantage is that several instances of Fiasco-UX can run in parallel.

We will now discuss in more detail the features of Fiasco that are relevant to our research.

#### 2.3.3Threads

Besides implementing the L4 thread specification, Fiasco also implements some additional mechanisms for performance- and real-time support purposes. Some of the performance optimizations stem from [Lie93].

$<sup>^{17}</sup>$ Execution can be interrupted at almost any time, which means the work is temporarily halted in favor of (at that moment) higher priority work. After the prioritized work has finished, the system continues with the interrupted execution.

$<sup>^{18}\</sup>mathrm{Dresden}$  Real-time OPerating Systems project.

#### Scheduling

As the L4 specification dictates, a thread has properties such as a time quantum and priority associated with it; these properties of a thread are called its *scheduling context* and are used in the scheduling of threads. To support the real-time features of Fiasco, each thread can also have an additional real-time scheduling context<sup>19</sup>. An *execution context* is a runnable, schedulable thread. At all times there is only one active execution context (or thread), as Fiasco does not support multi-processor execution (it will only use one of the processors available). A thread's current state of execution is stored in its thread control block (TCB), which resides in the kernel. Switching execution of threads can therefore be done through a simple TCB switch. The scheduler uses the *ready-list* (containing all threads ready to be run) to decide what thread to run next. More details on scheduling in Fiasco can be found in [Ste04].

#### **Ready-list**

As said, the system keeps a list of all threads ready to be executed: the ready-list. Although it might seem odd at first, the ready-list can contain threads that are *not* ready to be executed. If the scheduler finds such a thread while traversing the ready-list, it is immediately removed from it. The goal of this *lazy-scheduling* is improving the performance of IPC. As an example, we look at a call to the *call* IPC function, in which a sender sends a message to a receiver and then waits for that receiver to send a message back. If we were to strictly adhere to the property that the ready-list only contains ready threads, this IPC call would result in the following modifications to the ready-list:

- After the sender has sent its message, the sender enters a waiting mode and has to be dequeued.

- After the sender has sent its message, the receiver becomes ready and has to be enqueued.

- After the receiver has sent its message, the receiver enters a waiting mode and has to be dequeued.

- After the receiver has sent its message, the sender becomes ready and has to be enqueued.

We see that this common scenario results in four different changes to the ready-list. Obviously, this is detremental to IPC performance. However, if we allow non-ready threads in the ready-list and exclude the current executing thread from it (which is ready by definition), all four modifications can be saved. After the sender has sent its message, the receiver does not need to be enqueued as it has become the current executing thread. Similarly, once the receiver has sent its message back, the sender does not need to be enqueued as it will be the currently executing thread. Both dequeue actions can be saved as we allow threads in the ready-list that are not ready, which is precisely what entering a waiting mode signifies. To successfully apply this lazy-scheduling, the kernel has to make sure that the current executing thread will be enqueued in the ready-list if it cannot finish its task within its timeslice. If we would leave out this clause, the current executing thread is not guaranteed to get scheduled again (remember that it is not contained in the ready-list while executing), which is necessary in order to finish its task.

To switch execution from sender to receiver (and vice versa) without ready-list scheduling, the system uses their execution contexts. Say we want to switch execution from thread A (which is the current active thread) to thread B, but without using the ready-list. To do so, a simple switch of execution context from A to B suffices, as the current execution context determines what is executed. It is not necessary to also switch the scheduling context from A to B, in fact it is better not to for the following reason. If the scheduling context is not changed when the execution context is switched, thread B gets to execute as if it were A, which means that it can execute for the remainder of A's timeslice. This optimization gives B more execution time than it would normally have, thereby allowing it to finish sooner. In our *call* example, this means that after the sender has sent its message, an execution switch is made to the receiver which gets to execute in the sender's timeslice. Therefore, it is likely that the receiver is able to send a message back sooner, as the sender's timeslice remainder would otherwise be wasted by waiting on the receiver.

<sup>&</sup>lt;sup>19</sup>This is not part of the L4 specification.

In some situations, it might not be useful to immediately switch to the receiver but instead enqueue the receiver in the ready-list (which is the normal way in which a thread gets to execute). For this situation the *deceit-bit hack* can be used. Originally, the deceit-bit was used in the L4 clans & chiefs concept, but as this concept proved too inflexible it is almost never implemented. Therefore, the deceit-bit was *free* for other purposes and in Fiasco it is used to signal that no lazy-scheduling should be applied.

## 2.3.4 Synchronization

Having a fully preemptable system requires some form of synchronization for critical parts. Fiasco supports two different types of synchronization: *lock-free-* and *wait-free* synchronization. The main difference between the two synchronization types is in their intended use: lock-free synchronization should be used for time-critical synchronization (such as the synchronizing of frequently accessed, global data) and wait-free synchronization should be used for non time-critical operations (such as the synchronizing of local data). The two synchronization types are implemented as follows:

- Lock-free synchronization: this is achieved through atomic updating of memory<sup>20</sup>. It tries to exchange old data for new data and if this fails it simply retries. In order to prevent the system from retrying infinitely (which would invalidate the real-time properties of the system), a specific retry-count can be set. While setting the data, interrupts will be temporarily disabled to prevent another thread from modifying the data.

- Wait-free synchronization: this is a locking-type of synchronization, in which exclusive access to resources can be obtained by creating a lock. Fiasco expands on this well-known mechanism by introducing *switch locks* (also referred to as *helping locks*). Suppose thread A has locked a resource X which thread B also wants to access. Normally, B would just use up all of its execution time waiting on A to release the lock on X. However, instead of wasting execution time on waiting, B can also help A release its lock sooner by donating its remaining timeslice to A. Now A has more execution time available and will likely release the lock on X sooner, which is exactly what B wants. One might note the similarity of this optimization to the thread switch optimization in the ready-list description.

A full description of the design philosophy and implementation of these two synchronization mechanisms can be found in [HH01].

## 2.3.5 Locks

Wait-free synchronization in Fiasco can be achieved through the use of locks. Basically there are two types of locks: regular- and switch locks. Of the former there exists just one in Fiasco, namely the CPU lock, which temporarily disables interrupts. This lock should only be used for very short intervals as it can negatively influence the real-time features of the system. The other two locks in Fiasco are switch locks. The first switch lock is the thread lock, which locks access to a thread. The second switch lock is the helping lock, which is similar to the switch lock save from the fact that it also works when the scheduling system has not yet been loaded.

Switch locks are designed explicitly with IPC performance in mind; its basic optimization principle strongly resembles that discussed in the ready-list discussion. The implementation is as follows. When the current thread tries to acquire a lock on a resource by using a switch lock but detects that the resource is already locked, the lock count of the current thread is incremented. After incrementing the lock count, the switch lock keeps on switching to the lock owner (by switching the execution context to that of the lock owner) until the lock is free and can be acquired. Afterwards, when the lock is released, the lock count is decremented and the lock checks if it has been helped by another thread (which donated execution time to the thread holding the lock), if so it switches the execution context to that of the helper.

$<sup>^{20}\</sup>mathrm{The}$  x86 processor provides the compare-and-swap (CAS) instruction for exactly this purpose.

When a thread is locked, it will not be selected by the scheduler. Should a switch be made to a locked thread, the system will immediately switch to that thread's lock owner. Although locked threads normally do not get scheduled, an exception arises when a thread is killed. A thread that is to be killed should hold no locks at all, therefore the system keeps scheduling such a thread until it has released all its locks. The thread's lock count is used to determine if any locks are still present.

### 2.3.6 Timeouts

Fiasco recognizes three different types of timeouts: IPC-, deadline- and timeslice timeouts. An IPC timeout is used to restrict an IPC call to a specific maximum time, which can be used to prevent senders and receivers from waiting endlessly on each other. A deadline timeout is used to set timed deadlines and a timeslice timeout is used to signal the end of a timeslice.

Internally, timeouts are stored in a list that is ordered in ascending timeout order (the head of the list is the oldest timeout and the first to occur). When the system checks if timeouts occured, the timeout list can thus be traversed sequentially. Therefore, detecting timeouts is very fast whereas enqueuing or dequeuing is rather slow. For more details on the implementation of timeouts see [Reu05].

## 2.3.7 IPC

IPC in Fiasco supports all L4 IPC calls, namely *send*, *receive*, *wait*, *reply-wait* and *call*. All these functions are internally supported through one generic function:  $sys_ipc()$ , which parameters determine the actual call made. We will now describe the general setup of IPC in Fiasco.

#### Sender and receiver roles

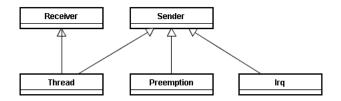

IPC in Fiasco is synchronous and thus always involves a single sender- and receiver communicating (sending messages) with each other. In Fiasco, there are separate definitions for the sender- and receiver roles. As threads need to both send- *and* receive messages, they extend (inherit from) both the receiver- and the sender role. In Fiasco, only threads extend the receiver role, in other words only threads can receive IPC messages. However, there are two more objects extending the sender role, namely the IRQ and preemption objects. The first translates hardware interrupts into IPC messages, which demonstrates the very generic applicability of Fiasco's receiver/sender setup. The second sends messages dealing with preemptions. As both the IRQ and preemption objects can only send messages (as they do not extend the receiver role), they are also known as *passive senders*.

Figure 2.1: Fiasco IPC roles diagram.

Due to IPC's synchronous nature, a receiver can only receive a message from a single sender. As it is possible that a receiver is unable to directly engage in IPC with a sender (for example because it is already engaged in IPC with another sender), the receiver should be able to queue send requests. This is achieved in Fiasco by letting the receiver have a sender list, which is a list of senders wanting to send a message to the receiver. Once a receiver engages in IPC with a sender, that sender is removed from the sender list (if he was it in). When an IPC call is made, the transferring of a message is handled from the viewpoint of the sender, it is the sender that determines which actions to do first and how to continue. An exception to this situation occurs when the sender is a passive sender; in this case the receiver controls IPC.

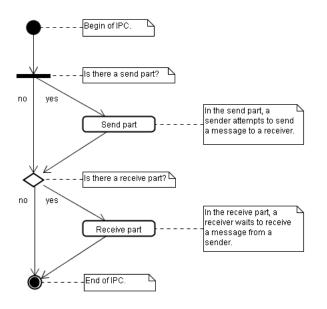

#### IPC overview

Although there are five different IPC calls, internally there is only one function that handles IPC:  $sys_ipc()$ . IPC (and thus the  $sys_ipc()$  function) can be divided into a send and receive part. Obviously, the send part handles the sending of an IPC message and the receive part handles the receiving thereof. The table below lists what IPC parts are involved in the five IPC calls:

| IPC call           | Send part | Receive part |

|--------------------|-----------|--------------|

| send               | x         | -            |

| receive            | -         | х            |

| wait               | -         | x            |

| $reply-wait\ call$ | x         | x            |

| call               | х         | x            |

Table 2.2: Mapping of L4 IPC calls to Fiasco send and receive parts.

The following schema gives an overview of how the send and receive parts are handled in Fiasco:

Figure 2.2: IPC overview.

One might remember that in the *reply-wait* and *call* calls, the message sending preceded the receiving of a message. In Fiasco, the receive part is handled *after* the send part to allow the aforementioned two calls to be handled in a single execution of the IPC path (this sequential structure has no influence on the functionality of the other three IPC calls).

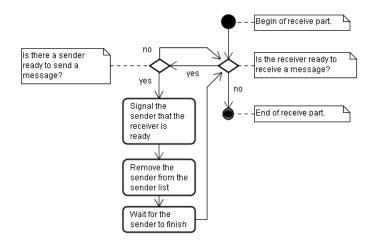

Before a message can be sent in the send part, the sender and receiver have to agree upon engaging in IPC; this is referred to as the *handshake*. It is possible that the receiver is not immediately ready to receive a message from the sender, for example because it is still engaged in IPC with another sender; in that case the sender is added to the receiver's sender list and waits for the receiver to become ready. If an error occured in the handshake, IPC is aborted. However, if the handshake was successful, the sender can then send its message to the receiver. The following scheme displays this set-up:

Figure 2.3: IPC send part overview.

As control of IPC is mostly handled by the sender (and thus in the send part), the receive part does relatively little. What *is* done in the receive part is that the receiver enters a loop. With each iteration, it checks if it is ready to receive a message and if there is a sender that wants to send a message (which is indicated by a non-empty sender list). If there is such a sender, the receiver sends it a signal to indicate that it is ready to receive a message. That sender is subsequently removed from the sender list by the receiver. Only when the receiver is not ready to receive a message is the receive part aborted.

Figure 2.4: IPC receive part overview.

#### **IPC** paths

Because IPC in Fiasco is unbuffered, no messages are temporarily stored by the kernel; instead messages are transferred directly between sender and receiver. As described in the L4 specification, Fiasco discerns between three different message types: untyped data (direct strings), memory-buffer references (indirect strings) and memory mappings (flexpages).

There are two paths in Fiasco through which an IPC message can be transferred: a short- and long IPC path.

- Short IPC path: this path uses only the system registers for transferring messages. The size of the data which can be transferred is thus limited to the size of the available registers. The advantages of only using the system registers for message transfer are that it is very fast and that no page-faults can occur (as no user-space memory is accessed). As an example of where the short IPC path is put to good use, when a page-fault IPC message is sent to a pager, that pager should respond with a flexpage IPC message to resolve the page-fault. Because a single flexpage does not exceed the size of the registers, it can be sent using the short IPC path allowing for a fast response by the pager. Secondly, when a direct string is sent, the system puts as much of that direct string into the registers; if the direct string does nog fit completely into the registers, the rest of the direct string is transferred using the long IPC path.

- Long IPC path: all message types can be transferred through the long IPC path, that includes indirect strings. Where the short IPC path limits the sending of flexpages to a single value, the long IPC path can send several flexpages at once. The transferring of messages is done by creating an IPC window. The IPC window is a part of the receiver's address space, which is mapped to the sender's address space during the message transfer. The sender can now directly copy the messages into the address space of the receiver, which prevents the kernel from buffering the messages. The main disadvantage of long IPC is that it has to invoke user-space memory, which could generate page-faults. A generated page-fault is sent to the pager of the receiver, as it is the receiver's address space that is being written to. Also, the long IPC path is slower than the short IPC path.

#### IPC shortcut path

Besides the two aforementioned IPC paths, there is also an IPC shortcut path. Basically, the IPC shortcut is an alternative version of the short IPC path (it thus also transfers messages through the system registers), but with some further restrictions applied to it (which enable performance optimizations). One of the restrictions of the shortcut is that it does not support the receive- and wait calls. Another restriction is that a single flexpage cannot be sent using the shortcut, only direct strings which fit into the registers are thus eligible for use with the IPC shortcut. Furthermore, the supported timeouts are limited to zero- (immediate response required) and infinite (no time-out at all) timeouts. The IPC shortcut completely runs with interrupts disabled.

The reason why the IPC shortcut was developed is simple: most of the system calls are IPC calls and most of the IPC messages are short IPC messages. Therefore, when the transfer of these short messages is optimized, the performance of the whole system is likely to improve significantly. There are two different versions of the shortcut. The normal version is implemented in C++, but there is also an optimized version of the shortcut, which is written in assembler and has been developed by Michael Peter [Pet02].

#### **IPC** states

The state of an IPC operation is stored at the receiver; this state is stored as a bit mask in which each bit corresponds to a specific state the thread can be in (for example waiting for a receiver or sending an IPC message). There are several functions to modify the state, which can add-, delete-or at once add- and delete bits in the state. These functions are respectively  $state_add()$ ,  $state_del()$  and  $state_change()$ . All these functions are atomic operations, which means that they are guaranteed

to succeed. The disadvantage of these atomic operations is that they are unnecessarily expensive when interrupts are already disabled. In this case regular operations would have exactly the same result as they too are then guaranteed to succeed, but without incurring the performance penalty of atomic operations. Fiasco therefore offers non-atomic variants of the state modification functions which are suffixed with "\_dirty" (leading to the *state\_add\_dirty()*, *state\_del\_dirty()* and *state\_change\_dirty()* functions). Please note that these *dirty* functions assume that interrupts are disabled, they do not check this themselves; it is therefore the responsibility of the caller to make sure interrupts are disabled when calling these functions.

#### Priority inversion

One of the classic scheduling problems is priority inversion, where a lower priority task is prioritized over a higher priority task. This situation occurs when a lower priority task has locked a shared resource that a higher priority task also wants to access. The higher priority task has no choice but to wait for the lower priority task to release the lock; the priorities are thus temporarily inversed. In Fiasco's old IPC path this problem existed when a combined send- and wait call was made. Let us consider a situation in which a sender A is engaged in a combined send- and wait operation with receiver B. As soon as A has sent its message to B, sender A enters a waiting state and an immediate execution context switch is made to receiver B (this optimization is described in the ready-list section). Because the receiver B gets to execute in the scheduling context of A, it will temporarily inherit the priority of A. Now suppose just before the switch to B, a second sender (which we call C) tries to send a message to B. If the priority than B, the switch from B to A (which has B's priority) violates the priority-based scheduling invariant<sup>21</sup>.

This problem was fixed in the current IPC implementation; its solution was actually quite simple: before switching to the receiver, the sender should check if there is a sender with a higher priority than its own that wants to send a message to the same receiver. Should this be the case, the receiver is added to the ready-list and the system switches to the higher priority sender. If no other higher priority sender exists, the immediate switch to the receiver can be done without any problem.

#### Real-time features

Because IPC is of vital importance to the performance of Fiasco (in fact, it is of vital performance to *any* microkernel), improving IPC is thus one of the key performance improving strategies. However, with Fiasco a constant eye has to kept at the real-time features of the system. Often, there is a trade-off between performance and real-time support. This can clearly be seen in René Reusner's attempt to improve the performance of IPC in Fiasco, which includes clear graphs detailing the trade-off results [Reu05].

Probably the best example of such a performance versus real-time features trade-off is the decision on which parts of the IPC path should be non-interruptible. If one makes the IPC path non-interruptible, this prevents the use of synchronization mechanisms, which are required in an interruptible path and thus improves performance. The real-time features are invalidated though. The current IPC path is non-interruptible in the following phases: the setup, rendez-vous and finish phase. Furthermore, when sending direct strings in the register transfer (short IPC) phase, the system remains non-interruptible. However, when a flexpage is sent in the register transfer phase or the memory transfer phase is used, the system *is* interruptible. An interruptible path has good real-time features, but this comes at the cost of decreased performance.

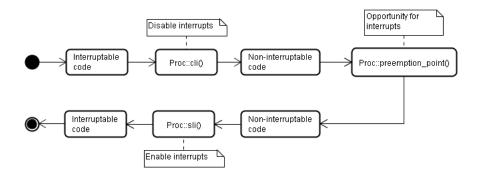

Although most phases are non-interruptible, in- and between phases interrupt points and -regions have been inserted to preserve the real-time features. An interrupt region is created by calling Proc::sti() (enable interrupts) at the beginning- and Proc::cli() (disable interrupts) at the end of the region. An

$<sup>^{21}</sup>$ Which states that higher priority threads should always be scheduled before lower priority threads.